33:

2048:

196:

227:). In more complex instances of the architecture, separate QPI link pairs connect one or more processors and one or more IO hubs or routing hubs in a network on the motherboard, allowing all of the components to access other components via the network. As with HyperTransport, the QuickPath Architecture assumes that the processors will have integrated

254:

operate using 10+1 or even 5+1 remaining signals, even reassigning the clock to a data signal if the clock fails. The initial

Nehalem implementation used a full four-quadrant interface to achieve 25.6 GB/s (6.4GT/s × 1 byte × 4), which provides exactly double the theoretical bandwidth of Intel's 1600 MHz FSB used in the X48 chipset.

250:, which has 8 bits for error detection, 8 bits for "link-layer header", and 64 bits for data. One 80-bit flit is transferred in two clock cycles (four 20-bit transfers, two per clock tick.) QPI bandwidths are advertised by computing the transfer of 64 bits (8 bytes) of data every two clock cycles in each direction.

398:

The routing layer sends a 72-bit unit consisting of an 8-bit header and a 64-bit payload. The header contains the destination and the message type. When the routing layer receives a unit, it examines its routing tables to determine if the unit has reached its destination. If so it is delivered to the

336:

Intel describes the data throughput (in GB/s) by counting only the 64-bit data payload in each 80-bit flit. However, Intel then doubles the result because the unidirectional send and receive link pair can be simultaneously active. Thus, Intel describes a 20-lane QPI link pair (send and receive) with

405:

The transport layer is not needed and is not present in devices that are intended for only point-to-point connections. This includes the Core i7. The transport layer sends and receives data across the QPI network from its peers on other devices that may not be directly connected (i.e., the data may

386:

The link layer is responsible for sending and receiving 80-bit flits. Each flit is sent to the physical layer as four 20-bit phits. Each flit contains an 8-bit CRC generated by the link layer transmitter and a 72-bit payload. If the link layer receiver detects a CRC error, the receiver notifies the

379:

The physical layer comprises the actual wiring and the differential transmitters and receivers, plus the lowest-level logic that transmits and receives the physical-layer unit. The physical-layer unit is the 20-bit "phit." The physical layer transmits a 20-bit "phit" using a single clock edge on 20

329:

the QPI operates at a clock rate of 2.4 GHz, 2.93 GHz, 3.2 GHz, 3.6 GHz, 4.0 GHz or 4.8 GHz (3.6 GHz and 4.0 GHz frequencies were introduced with the Sandy Bridge-E/EP platform and 4.8 GHz with the

Haswell-E/EP platform). The clock rate for a particular

253:

Although the initial implementations use single four-quadrant links, the QPI specification permits other implementations. Each quadrant can be used independently. On high-reliability servers, a QPI link can operate in a degraded mode. If one or more of the 20+1 signals fails, the interface will

391:

using a credit/debit scheme to prevent the receiver's buffer from overflowing. The link layer supports six different classes of message to permit the higher layers to distinguish data flits from non-data messages primarily for maintenance of cache coherence. In complex implementations of the

380:

lanes when all 20 lanes are available, or on 10 or 5 lanes when the QPI is reconfigured due to a failure. Note that in addition to the data signals, a clock signal is forwarded from the transmitter to receiver (which simplifies clock recovery at the expense of additional pins).

399:

next-higher layer. If not, it is sent on the correct outbound QPI. On a device with only one QPI, the routing layer is minimal. For more complex implementations, the routing layer's routing tables are more complex, and are modified dynamically to avoid failed QPI links.

330:

link depends on the capabilities of the components at each end of the link and the signal characteristics of the signal path on the printed circuit board. The non-extreme Core i7 9xx processors are restricted to a 2.4 GHz frequency at stock reference clocks.

372:, with separate physical, link, routing, transport, and protocol layers. In devices intended only for point-to-point QPI use with no forwarding, such as the Core i7-9xx and Xeon DP processors, the transport layer is not present and the routing layer is minimal.

337:

a 3.2 GHz clock as having a data rate of 25.6 GB/s. A clock rate of 2.4 GHz yields a data rate of 19.2 GB/s. More generally, by this definition a two-link 20-lane QPI transfers eight bytes per clock cycle, four in each direction.

392:

QuickPath architecture, the link layer can be configured to maintain separate flows and flow control for the different classes. It is not clear if this is needed or implemented for single-processor and dual-processor implementations.

918:

945:

412:

The protocol layer sends and receives packets on behalf of the device. A typical packet is a memory cache row. The protocol layer also participates in maintenance of cache coherence by sending and receiving relevant

880:

915:

772:

942:

687:

891:

313:

processors (as it was on

Clarkdale, for example), the internal ring interconnect between on-die cores is also based on the principles behind QPI, at least as far as

841:

97:, and certain desktop platforms starting in 2008. It increased the scalability and available bandwidth. Prior to the name's announcement, Intel referred to it as

970:

497:

758:

615:

406:

have been routed through an intervening device.) the transport layer verifies that the data is complete, and if not, it requests retransmission from its peer.

576:

1488:

1154:

1118:

1008:

257:

Although some high-end Core i7 processors expose QPI, other "mainstream" Nehalem desktop and mobile processors intended for single-socket boards (e.g.

2016:

1196:

1645:

246:, so the total number of pins is 84. The 20 data lanes are divided onto four "quadrants" of 5 lanes each. The basic unit of transfer is the 80-bit

1508:

937:

515:

1315:

1241:

1696:

1367:

219:. In its simplest form on a single-processor motherboard, a single QPI is used to connect the processor to the IO Hub (e.g., to connect an

776:

2043:

Interfaces are listed by their speed in the (roughly) ascending order, so the interface at the end of each section should be the fastest.

269:

and successor families) do not expose QPI externally, because these processors are not intended to participate in multi-socket systems.

1749:

1588:

1518:

1226:

1184:

147:(AMD) since around 2003. Intel developed QPI at its Massachusetts Microprocessor Design Center (MMDC) by members of what had been the

1578:

855:

589:

1676:

280:

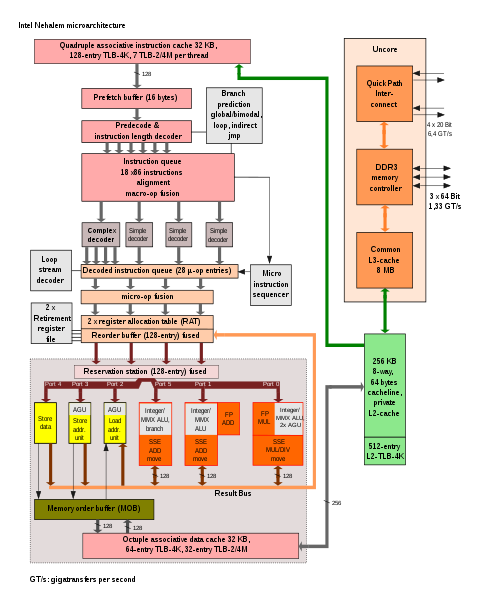

and GPU, if present; the uncore may or may not be on the same die as the CPU core, for instance it is on a separate die in the

1468:

1211:

1001:

820:

2020:

1671:

1640:

1266:

728:

713:

641:

541:

333:

Bit transfers occur on both the rising and the falling edges of the clock, so the transfer rate is double the clock rate.

177:

152:

120:

1113:

306:

Thus, there is no need to incur the expense of exposing the (former) front-side bus interface via the processor socket.

281:

266:

1944:

1883:

1738:

1402:

1201:

967:

494:

387:

transmitter via a flit on the return link of the pair and the transmitter resends the flit. The link layer implements

204:

170:

159:

124:

1543:

1308:

1057:

285:

262:

247:

1598:

994:

438:

232:

295:

In post-2009 single-socket chips starting with

Lynnfield, Clarksfield, Clarkdale and Arrandale, the traditional

1221:

955:

799:"QPI, Integrated Memory, PCI Express, And LGA 1156 - Intel Core i5 And Core i7: Intel's Mainstream Magnum Opus"

2075:

2070:

2051:

2026:

1918:

1573:

1293:

1261:

1251:

1179:

296:

1608:

1282:

1206:

1072:

1047:

300:

243:

144:

139:

Although sometimes called a "bus", QPI is a point-to-point interconnect. It was designed to compete with

2080:

1872:

1825:

1681:

1453:

1301:

1256:

1108:

423:

78:

773:"Intel Demonstrates Industry's First 32nm Chip and Next-Generation Nehalem Microprocessor Architecture"

916:

Transitioning the Intel® Next

Generation Microarchitectures (Nehalem and Westmere) into the Mainstream

299:

functions are integrated into these processors, which therefore communicate externally via the slower

1868:

1721:

1603:

1780:

1335:

388:

326:

1324:

1189:

707:

635:

535:

798:

151:

Development Group, which Intel had acquired from Compaq and HP and in turn originally came from

1770:

1392:

1328:

1164:

1123:

835:

228:

470:

242:), with a separate clock pair in each direction, for a total of 42 signals. Each signal is a

1503:

1174:

1067:

1633:

1483:

1463:

1338:

1231:

1052:

974:

949:

922:

501:

314:

109:

577:

SoftPedia: Intel Plans to

Replace Xeon with Its New Skylake-Based “Purley” Super Platform

980:

661:

46:

Please help update this article to reflect recent events or newly available information.

1934:

1628:

1553:

1478:

1382:

1357:

433:

428:

140:

86:

75:

2064:

2006:

1893:

1785:

1733:

1716:

1498:

1397:

1387:

1362:

1077:

220:

1743:

1686:

1538:

1443:

1082:

960:

310:

195:

238:

Each QPI comprises two 20-lane point-to-point data links, one in each direction (

2011:

1990:

1913:

1908:

1753:

1691:

1666:

1593:

1377:

1372:

1087:

443:

277:

239:

736:

1864:

1563:

1352:

1169:

1128:

1042:

184:

1888:

1878:

1845:

1840:

1775:

1650:

1438:

1423:

1418:

1236:

1216:

1092:

1062:

556:

369:

289:

224:

173:

in March 2009 and

Itanium processors in February 2010 (code named Tukwila).

163:

148:

105:). Earlier incarnations were known as Yet Another Protocol (YAP) and YAP+.

856:"Intel Clarkdale 32nm CPU-and-GPU chip benchmarked (again) - CPU - Feature"

1898:

1835:

1568:

1428:

1037:

1032:

258:

128:

353:× 2 (unidirectional send and receive operating simultaneously)

272:

However, QPI is used internally on these chips to communicate with the "

158:

Intel first delivered it for desktop processors in

November 2008 on the

2031:

1985:

1969:

1795:

1613:

1558:

1493:

1448:

448:

309:

Although the core–uncore QPI link is not present in desktop and mobile

166:

94:

881:"2nd Generation Intel Core Processor Family: Intel Core i7, i5 and i3"

1964:

1855:

1830:

1820:

1815:

1810:

1805:

1623:

1513:

1473:

1433:

276:", which is part of the chip containing memory controllers, CPU-side

273:

200:

113:

1949:

1860:

590:"Everything You Need to Know About The QuickPath Interconnect (QPI)"

211:

The QPI is an element of a system architecture that Intel calls the

986:

17:

1959:

1850:

1790:

1728:

1701:

1583:

1533:

1458:

1138:

1133:

1017:

819:

Published on 25th

January 2010 by Richard Swinburne (2010-01-25).

194:

82:

1954:

1939:

1800:

1711:

1706:

1548:

1159:

181:

90:

1297:

990:

1903:

1528:

1523:

26:

108:

QPI 1.1 is a significantly revamped version introduced with

759:"Intel® Xeon® Processor Scalable Family Technical Overview"

155:(DEC). Its development had been reported as early as 2004.

662:"The Common System Interface: Intel's Future Interconnect"

981:

The Common System

Interface: Intel’s Future Interconnect

261:

Core i3, Core i5, and other Core i7 processors from the

516:"Intel CSI name revealed: Slow, slow, quick quick slow"

616:"Intel Intel gets knickers in a twist over Tanglewood"

471:"An Introduction to the Intel QuickPath Interconnect"

1999:

1978:

1927:

1763:

1659:

1411:

1345:

1275:

1147:

1101:

1025:

938:

An Introduction to the Intel QuickPath Interconnect

874:

872:

622:. Archived from the original on September 3, 2010

968:First Look at Nehalem Microarchitecture: QPI Bus

688:"Intel's Whitefield takes four core IA-32 shape"

169:. It was released in Xeon processors code-named

1646:Coherent Accelerator Processor Interface (CAPI)

956:What you need to know about Intel’s Nehalem CPU

1309:

1002:

821:"Feature - Intel GMA HD Graphics Performance"

522:. Archived from the original on June 10, 2012

8:

694:. Archived from the original on May 24, 2009

840:: CS1 maint: numeric names: authors list (

729:"Intel's Tukwila Confirmed to be Quad Core"

655:

653:

651:

465:

463:

1316:

1302:

1294:

1155:Advanced Programmable Interrupt Controller

1119:Intel Communication Streaming Architecture

1009:

995:

987:

1197:High-bandwidth Digital Content Protection

63:Processor interconnect developed by Intel

977:, November 2, 2008, by Ilya Gavrichenkov

350:× 16(20) (data bits/QPI link width)

614:Charlie Demerjian (December 13, 2005).

459:

1242:Platform Environment Control Interface

833:

705:

633:

533:

943:Intel QuickPath Interconnect Overview

476:. Intel Corporation. January 30, 2009

7:

1227:Host Embedded Controller Interface

983:, August 28, 2007, by David Kanter

588:Gabriel Torres (August 25, 2008).

25:

340:The rate is computed as follows:

215:that implements what Intel calls

2047:

2046:

660:David Kanter (August 28, 2007).

347:× 2 bits/Hz (double data rate)

31:

925:, Hot Chips 21, August 24, 2009

686:Eva Glass (December 12, 2004).

964:, April 9, 2008, by Jon Stokes

1:

1641:Intel Ultra Path Interconnect

797:Chris Angelini (2009-09-07).

178:Intel Ultra Path Interconnect

153:Digital Equipment Corporation

127:-SP Xeon processors based on

121:Intel Ultra Path Interconnect

1619:Intel QuickPath Interconnect

1609:Direct Media Interface (DMI)

1185:Active Management Technology

1114:MultiProcessor Specification

914:Lily Looi, Stephan Jourdan,

727:David Kanter (May 5, 2006).

557:"Intel's Quick Path Evolved"

303:and PCI Express interfaces.

68:Intel QuickPath Interconnect

555:David Kanter (2011-07-20).

504:, retrieved August 21, 2007

2097:

1604:Compute Express Link (CXL)

879:Oded Lempel (2013-07-28).

514:Eva Glass (May 16, 2007).

2040:

1841:IEEE-1284 (parallel port)

1756:logical device interface)

712:: CS1 maint: unfit URL (

640:: CS1 maint: unfit URL (

540:: CS1 maint: unfit URL (

439:List of device bandwidths

356:÷ 8 (bits/byte)

233:non-uniform memory access

176:It was supplanted by the

40:This article needs to be

1222:Serial Digital Video Out

1212:Rapid Storage Technology

321:Frequency specifications

180:starting in 2017 on the

1267:Ultra Path Interconnect

1252:Platform Controller Hub

1180:Intel Management Engine

858:. HEXUS.net. 2009-09-25

370:five-layer architecture

99:Common System Interface

1403:List of bus bandwidths

1283:Silicon Photonics Link

1247:QuickPath Interconnect

368:QPI is specified as a

213:QuickPath architecture

208:

145:Advanced Micro Devices

143:that had been used by

74:) is a point-to-point

1257:System Management Bus

1202:High Definition Audio

1109:Common Building Block

424:Elastic interface bus

235:(NUMA) architecture.

203:component in Intel's

198:

1846:IEEE-1394 (FireWire)

1584:PCI Extended (PCI-X)

217:QuickPath technology

119:QPI was replaced by

1687:Parallel ATA (PATA)

559:. Realworldtech.com

327:synchronous circuit

85:which replaced the

1594:PCI Express (PCIe)

973:2016-05-14 at the

948:2014-02-02 at the

921:2020-08-02 at the

801:. Tomshardware.com

500:2013-10-17 at the

229:memory controllers

209:

207:microarchitecture.

2058:

2057:

2044:

1771:Apple Desktop Bus

1748:PCI Express (via

1707:Serial ATA (SATA)

1393:Network on a chip

1291:

1290:

1165:Intel Turbo Boost

1124:Intel Inboard 386

244:differential pair

160:Intel Core i7-9xx

61:

60:

16:(Redirected from

2088:

2050:

2049:

2042:

1504:HP Precision Bus

1318:

1311:

1304:

1295:

1207:Hub Architecture

1175:Intel Secure Key

1011:

1004:

997:

988:

926:

912:

906:

905:

903:

902:

896:

890:. Archived from

885:

876:

867:

866:

864:

863:

852:

846:

845:

839:

831:

829:

828:

816:

810:

809:

807:

806:

794:

788:

787:

785:

784:

775:. Archived from

769:

763:

762:

755:

749:

748:

746:

744:

735:. Archived from

724:

718:

717:

711:

703:

701:

699:

683:

677:

676:

674:

672:

657:

646:

645:

639:

631:

629:

627:

611:

605:

604:

602:

600:

594:Hardware Secrets

585:

579:

574:

568:

567:

565:

564:

552:

546:

545:

539:

531:

529:

527:

511:

505:

495:DailyTech report

492:

486:

485:

483:

481:

475:

467:

231:, and enables a

56:

53:

47:

35:

34:

27:

21:

2096:

2095:

2091:

2090:

2089:

2087:

2086:

2085:

2061:

2060:

2059:

2054:

2045:

2036:

1995:

1974:

1923:

1836:IEEE-488 (GPIB)

1759:

1655:

1634:Infinity Fabric

1464:Europe Card Bus

1407:

1341:

1322:

1292:

1287:

1271:

1232:Hyper-threading

1143:

1097:

1021:

1015:

975:Wayback Machine

950:Wayback Machine

934:

929:

923:Wayback Machine

913:

909:

900:

898:

894:

883:

878:

877:

870:

861:

859:

854:

853:

849:

832:

826:

824:

818:

817:

813:

804:

802:

796:

795:

791:

782:

780:

771:

770:

766:

757:

756:

752:

742:

740:

739:on May 10, 2012

733:Real World Tech

726:

725:

721:

704:

697:

695:

685:

684:

680:

670:

668:

666:Real World Tech

659:

658:

649:

632:

625:

623:

613:

612:

608:

598:

596:

587:

586:

582:

575:

571:

562:

560:

554:

553:

549:

532:

525:

523:

513:

512:

508:

502:Wayback Machine

493:

489:

479:

477:

473:

469:

468:

461:

457:

420:

402:Transport layer

366:

364:Protocol layers

323:

315:cache coherency

193:

137:

110:Sandy Bridge-EP

64:

57:

51:

48:

45:

36:

32:

23:

22:

15:

12:

11:

5:

2094:

2092:

2084:

2083:

2078:

2076:Intel products

2073:

2071:Computer buses

2063:

2062:

2056:

2055:

2041:

2038:

2037:

2035:

2034:

2029:

2024:

2014:

2009:

2003:

2001:

1997:

1996:

1994:

1993:

1988:

1982:

1980:

1976:

1975:

1973:

1972:

1967:

1962:

1957:

1952:

1947:

1945:Intel HD Audio

1942:

1937:

1935:ADAT Lightpipe

1931:

1929:

1925:

1924:

1922:

1921:

1916:

1911:

1906:

1901:

1896:

1891:

1886:

1881:

1876:

1858:

1853:

1848:

1843:

1838:

1833:

1828:

1823:

1818:

1813:

1808:

1803:

1798:

1793:

1788:

1783:

1778:

1773:

1767:

1765:

1761:

1760:

1758:

1757:

1746:

1741:

1736:

1731:

1726:

1725:

1724:

1719:

1709:

1704:

1699:

1694:

1689:

1684:

1679:

1674:

1669:

1663:

1661:

1657:

1656:

1654:

1653:

1648:

1643:

1638:

1637:

1636:

1629:HyperTransport

1626:

1621:

1616:

1611:

1606:

1601:

1596:

1591:

1586:

1581:

1576:

1571:

1566:

1561:

1556:

1551:

1546:

1541:

1536:

1531:

1526:

1521:

1516:

1511:

1506:

1501:

1496:

1491:

1486:

1481:

1476:

1471:

1466:

1461:

1456:

1451:

1446:

1441:

1436:

1431:

1426:

1421:

1415:

1413:

1409:

1408:

1406:

1405:

1400:

1395:

1390:

1385:

1383:Bus contention

1380:

1375:

1370:

1365:

1360:

1358:Front-side bus

1355:

1349:

1347:

1343:

1342:

1339:computer buses

1323:

1321:

1320:

1313:

1306:

1298:

1289:

1288:

1286:

1285:

1279:

1277:

1273:

1272:

1270:

1269:

1264:

1259:

1254:

1249:

1244:

1239:

1234:

1229:

1224:

1219:

1214:

1209:

1204:

1199:

1194:

1193:

1192:

1182:

1177:

1172:

1167:

1162:

1157:

1151:

1149:

1145:

1144:

1142:

1141:

1136:

1131:

1126:

1121:

1116:

1111:

1105:

1103:

1099:

1098:

1096:

1095:

1090:

1085:

1080:

1075:

1070:

1065:

1060:

1055:

1050:

1045:

1040:

1035:

1029:

1027:

1023:

1022:

1016:

1014:

1013:

1006:

999:

991:

985:

984:

978:

965:

953:

940:

933:

932:External links

930:

928:

927:

907:

868:

847:

823:. bit-tech.net

811:

789:

764:

750:

719:

678:

647:

606:

580:

569:

547:

506:

487:

458:

456:

453:

452:

451:

446:

441:

436:

434:HyperTransport

431:

429:Front-side bus

426:

419:

416:

415:

414:

410:

409:Protocol layer

407:

403:

400:

396:

393:

384:

381:

377:

376:Physical layer

365:

362:

361:

360:

357:

354:

351:

348:

345:

322:

319:

317:is concerned.

192:

191:Implementation

189:

141:HyperTransport

136:

133:

87:front-side bus

62:

59:

58:

39:

37:

30:

24:

14:

13:

10:

9:

6:

4:

3:

2:

2093:

2082:

2079:

2077:

2074:

2072:

2069:

2068:

2066:

2053:

2039:

2033:

2030:

2028:

2025:

2022:

2018:

2015:

2013:

2010:

2008:

2007:Multidrop bus

2005:

2004:

2002:

1998:

1992:

1989:

1987:

1984:

1983:

1981:

1977:

1971:

1968:

1966:

1963:

1961:

1958:

1956:

1953:

1951:

1948:

1946:

1943:

1941:

1938:

1936:

1933:

1932:

1930:

1926:

1920:

1917:

1915:

1914:External PCIe

1912:

1910:

1907:

1905:

1902:

1900:

1897:

1895:

1894:Parallel SCSI

1892:

1890:

1887:

1885:

1882:

1880:

1877:

1874:

1870:

1866:

1862:

1859:

1857:

1854:

1852:

1849:

1847:

1844:

1842:

1839:

1837:

1834:

1832:

1829:

1827:

1824:

1822:

1819:

1817:

1814:

1812:

1809:

1807:

1804:

1802:

1799:

1797:

1794:

1792:

1789:

1787:

1786:Commodore bus

1784:

1782:

1779:

1777:

1774:

1772:

1769:

1768:

1766:

1762:

1755:

1751:

1747:

1745:

1742:

1740:

1737:

1735:

1734:Fibre Channel

1732:

1730:

1727:

1723:

1720:

1718:

1715:

1714:

1713:

1710:

1708:

1705:

1703:

1700:

1698:

1695:

1693:

1690:

1688:

1685:

1683:

1680:

1678:

1675:

1673:

1670:

1668:

1665:

1664:

1662:

1658:

1652:

1649:

1647:

1644:

1642:

1639:

1635:

1632:

1631:

1630:

1627:

1625:

1622:

1620:

1617:

1615:

1612:

1610:

1607:

1605:

1602:

1600:

1597:

1595:

1592:

1590:

1587:

1585:

1582:

1580:

1577:

1575:

1572:

1570:

1567:

1565:

1562:

1560:

1557:

1555:

1552:

1550:

1547:

1545:

1542:

1540:

1537:

1535:

1532:

1530:

1527:

1525:

1522:

1520:

1517:

1515:

1512:

1510:

1507:

1505:

1502:

1500:

1497:

1495:

1492:

1490:

1487:

1485:

1482:

1480:

1477:

1475:

1472:

1470:

1467:

1465:

1462:

1460:

1457:

1455:

1452:

1450:

1447:

1445:

1442:

1440:

1437:

1435:

1432:

1430:

1427:

1425:

1422:

1420:

1417:

1416:

1414:

1410:

1404:

1401:

1399:

1398:Plug and play

1396:

1394:

1391:

1389:

1388:Bus mastering

1386:

1384:

1381:

1379:

1376:

1374:

1371:

1369:

1366:

1364:

1363:Back-side bus

1361:

1359:

1356:

1354:

1351:

1350:

1348:

1344:

1340:

1337:

1333:

1331:

1326:

1319:

1314:

1312:

1307:

1305:

1300:

1299:

1296:

1284:

1281:

1280:

1278:

1274:

1268:

1265:

1263:

1260:

1258:

1255:

1253:

1250:

1248:

1245:

1243:

1240:

1238:

1235:

1233:

1230:

1228:

1225:

1223:

1220:

1218:

1215:

1213:

1210:

1208:

1205:

1203:

1200:

1198:

1195:

1191:

1188:

1187:

1186:

1183:

1181:

1178:

1176:

1173:

1171:

1168:

1166:

1163:

1161:

1158:

1156:

1153:

1152:

1150:

1146:

1140:

1137:

1135:

1132:

1130:

1127:

1125:

1122:

1120:

1117:

1115:

1112:

1110:

1107:

1106:

1104:

1100:

1094:

1091:

1089:

1086:

1084:

1081:

1079:

1076:

1074:

1071:

1069:

1066:

1064:

1061:

1059:

1056:

1054:

1051:

1049:

1046:

1044:

1041:

1039:

1036:

1034:

1031:

1030:

1028:

1024:

1019:

1012:

1007:

1005:

1000:

998:

993:

992:

989:

982:

979:

976:

972:

969:

966:

963:

962:

957:

954:

951:

947:

944:

941:

939:

936:

935:

931:

924:

920:

917:

911:

908:

897:on 2020-07-29

893:

889:

882:

875:

873:

869:

857:

851:

848:

843:

837:

822:

815:

812:

800:

793:

790:

779:on 2008-01-02

778:

774:

768:

765:

760:

754:

751:

743:September 13,

738:

734:

730:

723:

720:

715:

709:

698:September 13,

693:

689:

682:

679:

667:

663:

656:

654:

652:

648:

643:

637:

626:September 13,

621:

617:

610:

607:

595:

591:

584:

581:

578:

573:

570:

558:

551:

548:

543:

537:

526:September 13,

521:

517:

510:

507:

503:

499:

496:

491:

488:

472:

466:

464:

460:

454:

450:

447:

445:

442:

440:

437:

435:

432:

430:

427:

425:

422:

421:

417:

411:

408:

404:

401:

397:

395:Routing layer

394:

390:

385:

382:

378:

375:

374:

373:

371:

363:

358:

355:

352:

349:

346:

343:

342:

341:

338:

334:

331:

328:

320:

318:

316:

312:

307:

304:

302:

298:

293:

291:

287:

283:

279:

275:

270:

268:

264:

260:

255:

251:

249:

245:

241:

236:

234:

230:

226:

222:

221:Intel Core i7

218:

214:

206:

202:

197:

190:

188:

186:

183:

179:

174:

172:

168:

165:

161:

156:

154:

150:

146:

142:

134:

132:

130:

126:

122:

117:

115:

111:

106:

104:

100:

96:

92:

88:

84:

81:developed by

80:

77:

73:

69:

55:

43:

38:

29:

28:

19:

2081:Serial buses

1618:

1539:TURBOchannel

1329:

1246:

1190:AMT versions

1102:Discontinued

961:Ars Technica

959:

910:

899:. Retrieved

892:the original

888:hotchips.org

887:

860:. Retrieved

850:

825:. Retrieved

814:

803:. Retrieved

792:

781:. Retrieved

777:the original

767:

753:

741:. Retrieved

737:the original

732:

722:

696:. Retrieved

692:The Inquirer

691:

681:

669:. Retrieved

665:

624:. Retrieved

620:The Inquirer

619:

609:

597:. Retrieved

593:

583:

572:

561:. Retrieved

550:

524:. Retrieved

520:The Inquirer

519:

509:

490:

478:. Retrieved

389:flow control

367:

339:

335:

332:

324:

311:Sandy Bridge

308:

305:

294:

271:

256:

252:

237:

216:

212:

210:

187:platforms.

175:

157:

138:

118:

107:

102:

98:

79:interconnect

71:

67:

65:

52:January 2014

49:

41:

2012:CoreConnect

1991:ExpressCard

1919:Thunderbolt

1909:Camera Link

1692:Bus and Tag

1378:Address bus

1373:Control bus

1368:Daisy chain

1262:Thunderbolt

599:January 23,

444:PCI Express

359:= 25.6 GB/s

297:northbridge

278:PCI Express

267:Clarksfield

240:full duplex

116:platform).

2065:Categories

1865:ACCESS.bus

1764:Peripheral

1564:InfiniBand

1559:HP GSC bus

1353:System bus

1129:Intel Play

1068:Skulltrail

1038:Centrino 2

1020:technology

901:2014-01-21

862:2014-01-21

827:2014-01-21

805:2014-01-21

783:2007-12-31

671:August 14,

563:2014-01-21

455:References

383:Link layer

199:QPI is an

185:Skylake-SP

135:Background

1826:Lightning

1776:Atari SIO

1651:SpaceWire

1484:Zorro III

1424:S-100 bus

1419:SS-50 bus

1412:Standards

1332:standards

1325:Technical

1237:Omni-Path

1217:SpeedStep

1063:Ultrabook

1026:Platforms

708:cite news

636:cite news

536:cite news

413:messages.

290:Arrandale

286:Clarkdale

263:Lynnfield

123:(UPI) in

89:(FSB) in

76:processor

2052:Category

2027:Wishbone

2000:Embedded

1979:Portable

1899:Profibus

1831:DMX512-A

1717:Parallel

1569:Ethernet

1479:Zorro II

1429:Multibus

1330:de facto

1276:Upcoming

1033:Centrino

971:Archived

946:Archived

919:Archived

836:cite web

498:Archived

480:June 14,

418:See also

325:Being a

282:Westmere

259:LGA 1156

131:socket.

129:LGA 3647

2032:SLIMbus

1986:PC Card

1970:TOSLINK

1660:Storage

1614:RapidIO

1494:FASTBUS

1449:STD Bus

1346:General

1148:Current

1078:Galileo

449:RapidIO

344:3.2 GHz

284:-based

205:Nehalem

171:Nehalem

167:chipset

125:Skylake

95:Itanium

42:updated

1965:S/PDIF

1856:1-Wire

1821:RS-485

1816:RS-423

1811:RS-422

1806:RS-232

1667:ST-506

1624:NVLink

1474:STEbus

1434:Unibus

1083:Edison

1053:Tablet

274:uncore

223:to an

201:uncore

114:Romley

1960:McASP

1928:Audio

1873:SMBus

1869:PMBus

1851:UNI/O

1791:HP-IL

1744:SATAe

1729:ESCON

1702:HIPPI

1534:NuBus

1489:CAMAC

1459:Q-Bus

1454:SMBus

1439:VAXBI

1336:wired

1139:MMC-2

1134:MMC-1

1088:Curie

1018:Intel

952:(PDF)

895:(PDF)

884:(PDF)

474:(PDF)

149:Alpha

83:Intel

2017:AMBA

1955:MADI

1940:AES3

1801:MIDI

1754:NVMe

1750:AHCI

1712:SCSI

1697:DSSI

1672:ESDI

1549:SBus

1509:EISA

1444:MBus

1334:for

1327:and

1170:vPro

1160:CNVi

1058:CULV

1043:Viiv

842:link

745:2013

714:link

700:2013

673:2014

642:link

628:2013

601:2017

542:link

528:2013

482:2011

248:flit

182:Xeon

162:and

91:Xeon

66:The

2021:AXI

1950:I²S

1904:USB

1889:D²B

1884:SPI

1879:I3C

1861:I²C

1796:HIL

1781:DCB

1752:or

1739:SSA

1722:SAS

1682:SMD

1677:IPI

1599:AGP

1589:PXI

1579:PCI

1574:UPA

1554:VLB

1544:MCA

1529:VPX

1524:VXS

1519:VXI

1514:VME

1499:LPC

1469:ISA

1093:Evo

1073:NUC

1048:MID

301:DMI

225:X58

164:X58

103:CSI

72:QPI

18:QPI

2067::

1871:,

1867:,

958:,

886:.

871:^

838:}}

834:{{

731:.

710:}}

706:{{

690:.

664:.

650:^

638:}}

634:{{

618:.

592:.

538:}}

534:{{

518:.

462:^

292:.

93:,

2023:)

2019:(

1875:)

1863:(

1317:e

1310:t

1303:v

1010:e

1003:t

996:v

904:.

865:.

844:)

830:.

808:.

786:.

761:.

747:.

716:)

702:.

675:.

644:)

630:.

603:.

566:.

544:)

530:.

484:.

288:/

265:/

112:(

101:(

70:(

54:)

50:(

44:.

20:)

Text is available under the Creative Commons Attribution-ShareAlike License. Additional terms may apply.