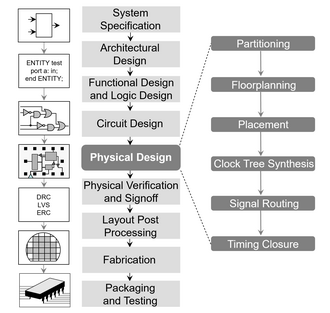

496:(CTO) clock can be shielded so that noise is not coupled to other signals. But shielding increases area by 12 to 15%. Since the clock signal is global in nature the same metal layer used for power routing is used for clock also. CTO is achieved by buffer sizing, gate sizing, buffer relocation, level adjustment and HFN synthesis. We try to improve setup slack in pre-placement, in placement and post placement optimization before CTS stages while neglecting hold slack. In post placement optimization after CTS hold slack is improved. As a result of CTS lot of buffers are added. Generally for 100k gates around 650 buffers are added.

467:) is to minimize skew and insertion delay. Clock is not propagated before CTS as shown in the picture. After CTS hold slack should improve. Clock tree begins at .sdc defined clock source and ends at stop pins of flop. There are two types of stop pins known as ignore pins and sync pins. 'Don't touch' circuits and pins in front end (logic synthesis) are treated as 'ignore' circuits or pins at back end (physical synthesis). 'Ignore' pins are ignored for timing analysis. If clock is divided then separate skew analysis is necessary.

33:

191:

141:. At this step, circuit representations of the components (devices and interconnects) of the design are converted into geometric representations of shapes which, when manufactured in the corresponding layers of materials, will ensure the required functioning of the components. This geometric representation is called

357:

proceeds to design each module. These modules are linked together in the main module called the TOP LEVEL module. This kind of partitioning is commonly referred to as

Logical Partitioning. The goal of partitioning is to split the circuit such that the number of connections between partitions is minimized.

374:. Floorplanning is the process of identifying structures that should be placed close together, and allocating space for them in such a manner as to meet the sometimes conflicting goals of available space (cost of the chip), required performance, and the desire to have everything close to everything else.

356:

Partitioning is a process of dividing the chip into small blocks. This is done mainly to separate different functional blocks and also to make placement and routing easier. Partitioning can be done in the RTL design phase when the design engineer partitions the entire design into sub-blocks and then

377:

Based on the area of the design and the hierarchy, a suitable floorplan is decided upon. Floorplanning takes into account the macros used in the design, memory, other IP cores and their placement needs, the routing possibilities, and also the area of the entire design. Floorplanning also determines

182:

Each of the phases mentioned above has design flows associated with them. These design flows lay down the process and guide-lines/framework for that phase. The physical design flow uses the technology libraries that are provided by the fabrication houses. These technology files provide information

389:

are the subjects of trade-offs. This is due to limited routing resources, as the more resources used, the slower the operation. Optimizing for minimum area allows the design both to use fewer resources, and for greater proximity of the sections of the design. This leads to shorter interconnect

330:

Physical design is based on a netlist which is the end result of the synthesis process. Synthesis converts the RTL design usually coded in VHDL or

Verilog HDL to gate-level descriptions which the next set of tools can read/understand. This netlist contains information on the cells used, their

397:

Data paths are typically the areas of the design where multiple bits are processed in parallel with each bit being modified the same way with maybe some influence from adjacent bits. Example structures that make up data paths are Adders, Subtractors, Counters, Registers, and Muxes.

434:

In-placement optimization re-optimizes the logic based on VR. This can perform cell sizing, cell moving, cell bypassing, net splitting, gate duplication, buffer insertion, area recovery. Optimization performs iteration of setup fixing, incremental timing and congestion driven

485:

409:

Before the start of placement optimization all Wire Load Models (WLM) are removed. Placement uses RC values from

Virtual Route (VR) to calculate timing. VR is the shortest Manhattan distance between two pins. VR RCs are more accurate than WLM RCs.

342:

During the synthesis process, constraints are applied to ensure that the design meets the required functionality and speed (specifications). Only after the netlist is verified for functionality and timing it is sent for the physical design flow.

452:

305:

The ASIC physical design flow uses the technology libraries that are provided by the fabrication houses. Technologies are commonly classified according to minimal feature size. Standard sizes, in the order of miniaturization, are

244:

167:. The inputs to physical design are (i) a netlist, (ii) library information on the basic devices in the design, and (iii) a technology file containing the manufacturing constraints. Physical design is usually concluded by

230:

for Semi-Custom design flows. The reason being that one has the flexibility to design/modify design blocks from vendor provided libraries in ASIC. This flexibility is missing for Semi-Custom flows using FPGAs (e.g.

393:

As a general rule, data-path sections benefit most from floorplanning, whereas random logic, state machines, and other non-structured logic can safely be left to the placer section of the place and route software.

438:

Post placement optimization before CTS performs netlist optimization with ideal clocks. It can fix setup, hold, max trans/cap violations. It can do placement optimization based on global routing. It re does HFN

508:

in the physical design process, global routing and detailed routing. Global routing allocates routing resources that are used for connections. It also does track assignment for a particular net.

288:

These steps are just the basics. There are detailed PD flows that are used depending on the Tools used and the methodology/technology. Some of the tools/software used in the back-end design are:

390:

distances, fewer routing resources used, faster end-to-end signal paths, and even faster and more consistent place and route times. Done correctly, there are no negatives to floorplanning.

2214:

50:

292:

Cadence (Cadence

Encounter RTL Compiler, Encounter Digital Implementation, Cadence Voltus IC Power Integrity Solution, Cadence Tempus Timing Signoff Solution)

2283:

511:

Detailed routing does the actual connections. Different constraints that are to be taken care during the routing are DRC, wire length, timing etc.

256:

248:

223:

2650:

2288:

735:

668:

633:

1069:

97:

431:

Pre-placement

Optimization optimizes the netlist before placement, HFNs (High Fanout Nets) are collapsed. It can also downsize the cells.

567:

69:

532:

This also includes density verification at the full chip level...Cleaning density is a very critical step in the lower technology nodes

2232:

1027:

2242:

711:

609:

215:

116:

76:

2473:

2092:

766:

481:

Rigidity is the term coined in Astro to indicate the relaxation of constraints. Higher the rigidity tighter is the constraints.

1595:

145:. This step is usually split into several sub-steps, which include both design and verification and validation of the layout.

2237:

83:

54:

722:

A. Kahng, J. Lienig, I. Markov, J. Hu: "VLSI Physical Design: From Graph

Partitioning to Timing Closure", Springer (2022),

620:

A. Kahng, J. Lienig, I. Markov, J. Hu: "VLSI Physical Design: From Graph

Partitioning to Timing Closure", Springer (2022),

2308:

1861:

961:

951:

378:

the IO structure and aspect ratio of the design. A bad floorplan will lead to wastage of die area and routing congestion.

155:

2114:

2097:

1819:

1659:

1094:

1010:

983:

370:

65:

1411:

973:

703:

519:

Physical verification checks the correctness of the generated layout design. This includes verifying that the layout

2478:

2340:

2252:

1622:

1161:

2435:

2104:

1719:

1714:

1644:

1585:

1389:

1374:

1185:

1101:

549:

142:

130:

560:

Chip finishing, such as inserting company/chip labels and final structures (e.g., seal ring, filler structures),

2440:

2197:

2109:

1871:

1558:

1488:

1349:

1205:

1116:

990:

442:

Post placement optimization after CTS optimizes timing with propagated clock. It tries to preserve clock skew.

1533:

2405:

2370:

2298:

2257:

2209:

2067:

1886:

1844:

1809:

1789:

1553:

318:

They may be also classified according to major manufacturing approaches: n-Well process, twin-well process,

43:

1925:

1794:

1759:

1210:

1111:

1084:

1022:

90:

2606:

2390:

2273:

2087:

1893:

1866:

1856:

1824:

1814:

1779:

1694:

1639:

1634:

1617:

1563:

1401:

1354:

1215:

1079:

1000:

856:

545:

2560:

2415:

2375:

2129:

2082:

1903:

1851:

1774:

1764:

1664:

1627:

1607:

1538:

1528:

936:

926:

883:

861:

816:

759:

319:

184:

2355:

2278:

2187:

2072:

1920:

1898:

1804:

1784:

1649:

1508:

1493:

1406:

1173:

1126:

907:

471:

Global skew achieves zero skew between two synchronous pins without considering logic relationship.

2592:

2468:

2420:

2395:

1834:

1669:

1654:

1513:

1329:

1200:

1146:

878:

674:

149:

2620:

474:

Local skew achieves zero skew between two synchronous pins while considering logic relationship.

2575:

2545:

2350:

2303:

2159:

2149:

1970:

1965:

1960:

1930:

1769:

1754:

1709:

1699:

1684:

1679:

1612:

1548:

1543:

1446:

1281:

1178:

1156:

1106:

1064:

1054:

968:

846:

786:

731:

707:

664:

629:

605:

580:

211:

Full-Custom: Designer has full flexibility on the layout design, no predefined cells are used.

171:, in which amendments and additions to the chip layout are performed. This is followed by the

1590:

2550:

2515:

2490:

2203:

2177:

2139:

1945:

1881:

1829:

1734:

1724:

1704:

1580:

1498:

1451:

1421:

1396:

1364:

1324:

1264:

1195:

1034:

723:

656:

621:

585:

650:

2540:

2520:

2500:

2495:

2485:

2380:

2015:

2005:

1990:

1950:

1915:

1908:

1839:

1799:

1568:

1441:

1431:

1339:

1296:

1276:

1005:

956:

752:

295:

Synopsys (Design

Compiler, IC Compiler II, IC Validator, PrimeTime, PrimePower, PrimeRail)

183:

regarding the type of silicon wafer used, the standard-cells used, the layout rules (like

691:

477:

If clock is skewed intentionally to improve setup slack then it is known as useful skew.

2565:

2510:

2463:

2445:

2247:

1995:

1985:

1980:

1955:

1749:

1729:

1602:

1573:

1523:

1456:

1426:

1416:

1379:

1301:

1259:

1254:

1136:

1131:

1121:

1039:

1017:

851:

841:

138:

2644:

2570:

2555:

2535:

2458:

2360:

2192:

2182:

2010:

2000:

1975:

1940:

1503:

1436:

1359:

1334:

1286:

1271:

978:

898:

678:

505:

566:

Layout-to-mask preparation that extends layout data with graphics operations (e.g.,

2453:

2430:

2400:

2385:

1674:

1291:

1232:

1044:

995:

946:

921:

873:

866:

179:

where designs are transferred onto silicon dies which are then packaged into ICs.

2530:

2525:

2505:

2425:

2345:

2154:

2059:

1369:

1344:

1316:

1245:

1190:

1168:

916:

893:

888:

831:

826:

204:

32:

649:

J. Lienig, J. Scheible (2020). "Chap. 3.3: Mask Data: Layout Post

Processing".

17:

2627:

2144:

1739:

1518:

1240:

1220:

1074:

912:

727:

660:

625:

604:

N. Sherwani, "Algorithms for VLSI Physical Design

Automation", Kluwer (1998),

484:

309:

331:

interconnections, area used, and other details. Typical synthesis tools are:

2613:

2599:

2410:

2134:

2119:

2077:

1689:

1249:

1089:

553:

313:

190:

535:

Complies with all electrical requirements – Electrical Rule Checking (ERC).

218:) are used, designer has flexibility in placement of the cells and routing.

570:, RET) and adjusts the data to mask production devices (photomask writer).

1744:

791:

335:

Cadence RTL Compiler/Build Gates/Physically Knowledgeable Synthesis (PKS)

451:

2365:

2293:

903:

523:

Complies with all technology requirements – Design Rule Checking (DRC)

2124:

775:

232:

548:, often concludes physical design and verification. It converts the

526:

Is consistent with the original netlist – Layout vs. Schematic (LVS)

563:

Generating a reticle layout with test patterns and alignment marks,

423:

Post Placement Optimization (PPO) before clock tree synthesis (CTS)

243:

836:

483:

450:

242:

189:

1876:

227:

214:

Semi-Custom: Pre-designed library cells (preferably tested with

2329:

2032:

1477:

804:

748:

137:

is a step in the standard design cycle which follows after the

26:

702:

Mehrotra, Alok; Van Ginneken, Lukas P P P; Trivedi, Yatin.

744:

316:, 130nm, 90nm, 65nm, 45nm, 28nm, 22nm, 18nm, 14nm, etc.

203:

Typically, the IC physical design is categorized into

652:

Fundamentals of Layout Design for Electronic Circuits

413:

Placement is performed in four optimization phases:

2266:

2225:

2168:

2058:

1310:

1229:

1145:

1053:

935:

815:

57:. Unsourced material may be challenged and removed.

301:Mentor Graphics (Olympus SoC, IC-Station, Calibre)

552:(polygons) into mask data (instructions for the

284:Layout Post Processing with Mask Data Generation

704:"Design flow and methodology for 50M gate ASIC"

368:The second step in the physical design flow is

194:Physical design steps within the IC design flow

529:Has no antenna effects – Antenna Rule Checking

760:

644:

642:

8:

2326:

2055:

2029:

1474:

812:

801:

767:

753:

745:

117:Learn how and when to remove this message

2284:Good Design Award (Museum of Modern Art)

597:

2289:Good Design Award (Chicago Athenaeum)

7:

55:adding citations to reliable sources

568:resolution enhancement technologies

544:Layout Post Processing, also known

312:, 1μm , 0.5μm , 0.35μm, 0.25μm, 180

2233:American Institute of Graphic Arts

66:"Physical design" electronics

25:

2243:Design and Industries Association

263:Design Netlist (after synthesis)

31:

706:, IEEE Conference Publications,

42:needs additional citations for

2238:Chartered Society of Designers

381:In many design methodologies,

1:

2309:Prince Philip Designers Prize

952:Architectural lighting design

655:. Springer. p. 102-110.

152:(IC) design is split up into

2651:Electronic design automation

2115:Electronic design automation

2098:Virtual home design software

1070:Automotive suspension design

974:Environmental impact design

226:for Full Custom design and

2667:

2253:International Forum Design

1623:Engineering design process

417:Pre-placement optimization

275:Clock-tree Synthesis (CTS)

259:physical design flow are:

2588:

2336:

2325:

2054:

2028:

1484:

1473:

1375:Integrated circuit design

1297:Stage/set lighting design

1186:Hardware interface design

1102:Hardware interface design

811:

800:

782:

728:10.1007/978-3-030-96415-3

661:10.1007/978-3-030-39284-0

626:10.1007/978-90-481-9591-6

420:In placement optimization

298:Magma (BlastFusion, etc.)

239:ASIC physical design flow

143:integrated circuit layout

131:integrated circuit design

2210:Industrial design rights

2198:Fashion design copyright

2110:Design quality indicator

1559:Creative problem-solving

1350:Electrical system design

1206:Sonic interaction design

1117:Photographic lens design

991:Healthy community design

338:Synopsys Design Compiler

207:and semi-custom design.

2406:New product development

2371:Enterprise architecture

2299:IF Product Design Award

2258:Design Research Society

1810:Reliability engineering

692:Semi-Custom Design Flow

504:There are two types of

494:clock tree optimization

154:Front-end Design using

1862:Top-down and bottom-up

1211:User experience design

1112:Packaging and labeling

1085:Electric guitar design

1023:Landscape architecture

540:Layout post processing

489:

456:

455:Ideal clock before CTS

255:The main steps in the

252:

195:

169:Layout Post Processing

2391:Innovation management

2274:European Design Award

2040:Intellectual property

1857:Theory of constraints

1820:Responsibility-driven

1660:For manufacturability

1564:Creativity techniques

1402:Nuclear weapon design

1216:User interface design

1080:Corrugated box design

1001:Interior architecture

556:writer). It includes

546:mask data preparation

515:Physical verification

487:

454:

281:Physical Verification

246:

193:

177:Manufacturing Process

2436:Unintelligent design

2416:Philosophy of design

2130:Design specification

2083:Comprehensive layout

1655:For behaviour change

1628:Probabilistic design

1390:Power network design

927:Visual merchandising

884:Instructional design

862:Postage stamp design

461:clock tree synthesis

447:Clock tree synthesis

51:improve this article

2356:Creative industries

2279:German Design Award

2188:Design infringement

2073:Architectural model

1412:Organization design

1407:Nucleic acid design

1355:Experimental design

908:Traffic sign design

2421:Process simulation

2396:Intelligent design

1720:Intelligence-based

1715:Integrated topside

1645:Framework-oriented

1330:Behavioural design

1201:Information design

879:Information design

490:

457:

253:

196:

150:Integrated Circuit

2638:

2637:

2584:

2583:

2351:Conceptual design

2321:

2320:

2317:

2316:

2304:James Dyson Award

2160:Website wireframe

2150:Technical drawing

2024:

2023:

1872:Transgenerational

1613:Ecological design

1489:Activity-centered

1469:

1468:

1465:

1464:

1447:Spacecraft design

1241:Public art design

1179:Video game design

1157:Experience design

1127:Production design

1107:Motorcycle design

1065:Automotive design

969:Ecological design

847:Film title design

736:978-3-030-96414-6

670:978-3-030-39284-0

634:978-3-030-96414-6

127:

126:

119:

101:

16:(Redirected from

2658:

2630:

2623:

2616:

2609:

2602:

2595:

2327:

2204:Geschmacksmuster

2178:Community design

2056:

2030:

1790:Process-centered

1586:Design–bid–build

1554:Cradle-to-cradle

1534:Concept-oriented

1475:

1452:Strategic design

1422:Processor design

1397:Mechanism design

1365:Geometric design

1325:Algorithm design

1265:Jewellery design

1196:Immersive design

1090:Furniture design

1035:Landscape design

813:

802:

769:

762:

755:

746:

739:

720:

714:

700:

694:

689:

683:

682:

646:

637:

618:

612:

602:

122:

115:

111:

108:

102:

100:

59:

35:

27:

21:

2666:

2665:

2661:

2660:

2659:

2657:

2656:

2655:

2641:

2640:

2639:

2634:

2628:

2621:

2614:

2607:

2600:

2593:

2580:

2381:Futures studies

2332:

2313:

2262:

2221:

2170:

2164:

2050:

2049:

2020:

1926:Value sensitive

1916:User innovation

1795:Public interest

1760:Object-oriented

1480:

1461:

1442:Software design

1432:Research design

1385:Physical design

1340:Database design

1314:

1312:

1306:

1282:Property design

1277:Game art design

1231:

1225:

1148:

1141:

1056:

1049:

1006:Interior design

957:Building design

938:

931:

818:

807:

796:

778:

773:

743:

742:

721:

717:

701:

697:

690:

686:

671:

648:

647:

640:

619:

615:

603:

599:

594:

577:

550:physical layout

542:

517:

502:

488:Clock After CTS

449:

407:

401:

366:

360:

354:

349:

328:

241:

201:

187:in VLSI), etc.

165:Physical Design

161:Back-end Design

135:physical design

123:

112:

106:

103:

60:

58:

48:

36:

23:

22:

18:Back-end design

15:

12:

11:

5:

2664:

2662:

2654:

2653:

2643:

2642:

2636:

2635:

2633:

2632:

2625:

2618:

2611:

2604:

2597:

2589:

2586:

2585:

2582:

2581:

2579:

2578:

2573:

2568:

2563:

2558:

2553:

2548:

2543:

2538:

2533:

2528:

2523:

2518:

2513:

2508:

2503:

2498:

2493:

2488:

2483:

2482:

2481:

2476:

2466:

2461:

2456:

2449:

2448:

2446:Wicked problem

2443:

2438:

2433:

2428:

2423:

2418:

2413:

2408:

2403:

2398:

2393:

2388:

2383:

2378:

2373:

2368:

2363:

2358:

2353:

2348:

2343:

2337:

2334:

2333:

2331:Related topics

2330:

2323:

2322:

2319:

2318:

2315:

2314:

2312:

2311:

2306:

2301:

2296:

2291:

2286:

2281:

2276:

2270:

2268:

2264:

2263:

2261:

2260:

2255:

2250:

2248:Design Council

2245:

2240:

2235:

2229:

2227:

2223:

2222:

2220:

2219:

2218:

2217:

2215:European Union

2207:

2200:

2195:

2190:

2185:

2180:

2174:

2172:

2166:

2165:

2163:

2162:

2157:

2152:

2147:

2142:

2137:

2132:

2127:

2122:

2117:

2112:

2107:

2102:

2101:

2100:

2095:

2085:

2080:

2075:

2070:

2064:

2062:

2052:

2051:

2048:

2047:

2044:

2041:

2038:

2034:

2033:

2026:

2025:

2022:

2021:

2019:

2018:

2013:

2008:

2003:

1998:

1993:

1988:

1983:

1978:

1973:

1968:

1963:

1958:

1953:

1948:

1943:

1936:

1935:

1934:

1933:

1923:

1918:

1913:

1912:

1911:

1901:

1896:

1894:Usage-centered

1891:

1890:

1889:

1887:Design for All

1879:

1874:

1869:

1867:Transformation

1864:

1859:

1854:

1849:

1848:

1847:

1837:

1832:

1827:

1822:

1817:

1815:Research-based

1812:

1807:

1802:

1797:

1792:

1787:

1782:

1780:Platform-based

1777:

1772:

1767:

1762:

1757:

1752:

1747:

1742:

1737:

1732:

1730:KISS principle

1727:

1722:

1717:

1712:

1707:

1702:

1697:

1692:

1687:

1682:

1677:

1672:

1667:

1662:

1657:

1652:

1647:

1642:

1640:Fault-tolerant

1637:

1635:Error-tolerant

1632:

1631:

1630:

1620:

1618:Energy neutral

1615:

1610:

1605:

1600:

1599:

1598:

1588:

1583:

1578:

1577:

1576:

1574:Design fiction

1566:

1561:

1556:

1551:

1546:

1541:

1536:

1531:

1526:

1521:

1516:

1511:

1506:

1501:

1496:

1491:

1485:

1482:

1481:

1478:

1471:

1470:

1467:

1466:

1463:

1462:

1460:

1459:

1457:Systems design

1454:

1449:

1444:

1439:

1434:

1429:

1427:Protein design

1424:

1419:

1417:Process design

1414:

1409:

1404:

1399:

1394:

1393:

1392:

1387:

1382:

1380:Circuit design

1372:

1367:

1362:

1357:

1352:

1347:

1342:

1337:

1332:

1327:

1321:

1319:

1308:

1307:

1305:

1304:

1302:Textile design

1299:

1294:

1289:

1284:

1279:

1274:

1269:

1268:

1267:

1262:

1260:Costume design

1255:Fashion design

1252:

1243:

1237:

1235:

1227:

1226:

1224:

1223:

1218:

1213:

1208:

1203:

1198:

1193:

1188:

1183:

1182:

1181:

1176:

1166:

1165:

1164:

1153:

1151:

1143:

1142:

1140:

1139:

1137:Service design

1134:

1132:Sensory design

1129:

1124:

1122:Product design

1119:

1114:

1109:

1104:

1099:

1098:

1097:

1087:

1082:

1077:

1072:

1067:

1061:

1059:

1051:

1050:

1048:

1047:

1042:

1040:Spatial design

1037:

1032:

1031:

1030:

1020:

1018:Keyline design

1015:

1014:

1013:

1003:

998:

993:

988:

987:

986:

984:Computer-aided

976:

971:

966:

965:

964:

954:

949:

943:

941:

933:

932:

930:

929:

924:

919:

910:

901:

896:

891:

886:

881:

876:

871:

870:

869:

864:

859:

852:Graphic design

849:

844:

842:Exhibit design

839:

834:

829:

823:

821:

809:

808:

805:

798:

797:

795:

794:

789:

783:

780:

779:

774:

772:

771:

764:

757:

749:

741:

740:

715:

695:

684:

669:

638:

613:

596:

595:

593:

590:

589:

588:

583:

576:

573:

572:

571:

564:

561:

541:

538:

537:

536:

533:

530:

527:

524:

516:

513:

501:

498:

479:

478:

475:

472:

448:

445:

444:

443:

440:

436:

432:

428:

427:

426:PPO after CTS.

424:

421:

418:

406:

403:

365:

362:

353:

350:

348:

345:

340:

339:

336:

327:

326:Design netlist

324:

322:process, etc.

303:

302:

299:

296:

293:

286:

285:

282:

279:

276:

273:

270:

267:

264:

240:

237:

220:

219:

212:

200:

197:

139:circuit design

125:

124:

39:

37:

30:

24:

14:

13:

10:

9:

6:

4:

3:

2:

2663:

2652:

2649:

2648:

2646:

2631:

2626:

2624:

2619:

2617:

2612:

2610:

2605:

2603:

2598:

2596:

2591:

2590:

2587:

2577:

2574:

2572:

2569:

2567:

2564:

2562:

2561:specification

2559:

2557:

2554:

2552:

2549:

2547:

2544:

2542:

2539:

2537:

2534:

2532:

2529:

2527:

2524:

2522:

2519:

2517:

2514:

2512:

2509:

2507:

2504:

2502:

2499:

2497:

2494:

2492:

2489:

2487:

2484:

2480:

2477:

2475:

2474:architectural

2472:

2471:

2470:

2467:

2465:

2462:

2460:

2457:

2455:

2451:

2450:

2447:

2444:

2442:

2441:Visualization

2439:

2437:

2434:

2432:

2429:

2427:

2424:

2422:

2419:

2417:

2414:

2412:

2409:

2407:

2404:

2402:

2399:

2397:

2394:

2392:

2389:

2387:

2384:

2382:

2379:

2377:

2374:

2372:

2369:

2367:

2364:

2362:

2361:Cultural icon

2359:

2357:

2354:

2352:

2349:

2347:

2344:

2342:

2339:

2338:

2335:

2328:

2324:

2310:

2307:

2305:

2302:

2300:

2297:

2295:

2292:

2290:

2287:

2285:

2282:

2280:

2277:

2275:

2272:

2271:

2269:

2265:

2259:

2256:

2254:

2251:

2249:

2246:

2244:

2241:

2239:

2236:

2234:

2231:

2230:

2228:

2226:Organizations

2224:

2216:

2213:

2212:

2211:

2208:

2206:

2205:

2201:

2199:

2196:

2194:

2193:Design patent

2191:

2189:

2186:

2184:

2183:Design around

2181:

2179:

2176:

2175:

2173:

2167:

2161:

2158:

2156:

2153:

2151:

2148:

2146:

2143:

2141:

2138:

2136:

2133:

2131:

2128:

2126:

2123:

2121:

2118:

2116:

2113:

2111:

2108:

2106:

2103:

2099:

2096:

2094:

2091:

2090:

2089:

2086:

2084:

2081:

2079:

2076:

2074:

2071:

2069:

2066:

2065:

2063:

2061:

2057:

2053:

2045:

2043:Organizations

2042:

2039:

2036:

2035:

2031:

2027:

2017:

2014:

2012:

2009:

2007:

2004:

2002:

1999:

1997:

1994:

1992:

1989:

1987:

1984:

1982:

1979:

1977:

1974:

1972:

1969:

1967:

1964:

1962:

1959:

1957:

1954:

1952:

1949:

1947:

1944:

1942:

1938:

1937:

1932:

1929:

1928:

1927:

1924:

1922:

1919:

1917:

1914:

1910:

1907:

1906:

1905:

1904:User-centered

1902:

1900:

1897:

1895:

1892:

1888:

1885:

1884:

1883:

1880:

1878:

1875:

1873:

1870:

1868:

1865:

1863:

1860:

1858:

1855:

1853:

1852:Tableless web

1850:

1846:

1843:

1842:

1841:

1838:

1836:

1833:

1831:

1828:

1826:

1823:

1821:

1818:

1816:

1813:

1811:

1808:

1806:

1803:

1801:

1798:

1796:

1793:

1791:

1788:

1786:

1783:

1781:

1778:

1776:

1775:Participatory

1773:

1771:

1768:

1766:

1763:

1761:

1758:

1756:

1753:

1751:

1748:

1746:

1743:

1741:

1738:

1736:

1733:

1731:

1728:

1726:

1723:

1721:

1718:

1716:

1713:

1711:

1708:

1706:

1703:

1701:

1698:

1696:

1693:

1691:

1688:

1686:

1683:

1681:

1678:

1676:

1673:

1671:

1668:

1666:

1665:For Six Sigma

1663:

1661:

1658:

1656:

1653:

1651:

1648:

1646:

1643:

1641:

1638:

1636:

1633:

1629:

1626:

1625:

1624:

1621:

1619:

1616:

1614:

1611:

1609:

1608:Domain-driven

1606:

1604:

1601:

1597:

1596:architect-led

1594:

1593:

1592:

1589:

1587:

1584:

1582:

1579:

1575:

1572:

1571:

1570:

1567:

1565:

1562:

1560:

1557:

1555:

1552:

1550:

1547:

1545:

1542:

1540:

1539:Configuration

1537:

1535:

1532:

1530:

1527:

1525:

1522:

1520:

1517:

1515:

1512:

1510:

1507:

1505:

1504:Brainstorming

1502:

1500:

1497:

1495:

1492:

1490:

1487:

1486:

1483:

1476:

1472:

1458:

1455:

1453:

1450:

1448:

1445:

1443:

1440:

1438:

1437:Social design

1435:

1433:

1430:

1428:

1425:

1423:

1420:

1418:

1415:

1413:

1410:

1408:

1405:

1403:

1400:

1398:

1395:

1391:

1388:

1386:

1383:

1381:

1378:

1377:

1376:

1373:

1371:

1368:

1366:

1363:

1361:

1360:Filter design

1358:

1356:

1353:

1351:

1348:

1346:

1343:

1341:

1338:

1336:

1335:Boiler design

1333:

1331:

1328:

1326:

1323:

1322:

1320:

1318:

1309:

1303:

1300:

1298:

1295:

1293:

1290:

1288:

1287:Scenic design

1285:

1283:

1280:

1278:

1275:

1273:

1272:Floral design

1270:

1266:

1263:

1261:

1258:

1257:

1256:

1253:

1251:

1247:

1244:

1242:

1239:

1238:

1236:

1234:

1228:

1222:

1219:

1217:

1214:

1212:

1209:

1207:

1204:

1202:

1199:

1197:

1194:

1192:

1189:

1187:

1184:

1180:

1177:

1175:

1172:

1171:

1170:

1167:

1163:

1160:

1159:

1158:

1155:

1154:

1152:

1150:

1144:

1138:

1135:

1133:

1130:

1128:

1125:

1123:

1120:

1118:

1115:

1113:

1110:

1108:

1105:

1103:

1100:

1096:

1093:

1092:

1091:

1088:

1086:

1083:

1081:

1078:

1076:

1073:

1071:

1068:

1066:

1063:

1062:

1060:

1058:

1052:

1046:

1043:

1041:

1038:

1036:

1033:

1029:

1026:

1025:

1024:

1021:

1019:

1016:

1012:

1009:

1008:

1007:

1004:

1002:

999:

997:

994:

992:

989:

985:

982:

981:

980:

979:Garden design

977:

975:

972:

970:

967:

963:

962:Passive solar

960:

959:

958:

955:

953:

950:

948:

945:

944:

942:

940:

937:Environmental

934:

928:

925:

923:

920:

918:

914:

911:

909:

905:

902:

900:

899:Retail design

897:

895:

892:

890:

887:

885:

882:

880:

877:

875:

872:

868:

865:

863:

860:

858:

855:

854:

853:

850:

848:

845:

843:

840:

838:

835:

833:

830:

828:

825:

824:

822:

820:

817:Communication

814:

810:

803:

799:

793:

790:

788:

785:

784:

781:

777:

770:

765:

763:

758:

756:

751:

750:

747:

737:

733:

729:

725:

719:

716:

713:

712:0-7803-7659-5

709:

705:

699:

696:

693:

688:

685:

680:

676:

672:

666:

662:

658:

654:

653:

645:

643:

639:

635:

631:

627:

623:

617:

614:

611:

610:9780792383932

607:

601:

598:

591:

587:

584:

582:

579:

578:

574:

569:

565:

562:

559:

558:

557:

555:

551:

547:

539:

534:

531:

528:

525:

522:

521:

520:

514:

512:

509:

507:

499:

497:

495:

486:

482:

476:

473:

470:

469:

468:

466:

462:

453:

446:

441:

437:

433:

430:

429:

425:

422:

419:

416:

415:

414:

411:

404:

402:

399:

395:

391:

388:

384:

379:

375:

373:

372:

371:floorplanning

364:Floorplanning

363:

361:

358:

351:

346:

344:

337:

334:

333:

332:

325:

323:

321:

317:

315:

311:

300:

297:

294:

291:

290:

289:

283:

280:

277:

274:

271:

268:

266:Floorplanning

265:

262:

261:

260:

258:

251:back-end flow

250:

245:

238:

236:

234:

229:

225:

217:

213:

210:

209:

208:

206:

198:

192:

188:

186:

180:

178:

174:

170:

166:

162:

158:

157:

151:

146:

144:

140:

136:

132:

121:

118:

110:

107:December 2022

99:

96:

92:

89:

85:

82:

78:

75:

71:

68: –

67:

63:

62:Find sources:

56:

52:

46:

45:

40:This article

38:

34:

29:

28:

19:

2431:STEAM fields

2401:Lean startup

2386:Indie design

2202:

2169:Intellectual

1921:Value-driven

1899:Use-centered

1805:Regenerative

1785:Policy-based

1745:Mind mapping

1650:For assembly

1591:Design–build

1509:By committee

1494:Adaptive web

1384:

1292:Sound design

1250:glass design

1248: /

1233:applied arts

1174:Level design

1045:Urban design

996:Hotel design

947:Architecture

922:Video design

915: /

906: /

874:Illustration

867:Print design

837:Brand design

718:

698:

687:

651:

616:

600:

543:

518:

510:

503:

493:

491:

480:

464:

460:

459:The goal of

458:

412:

408:

400:

396:

392:

386:

382:

380:

376:

369:

367:

359:

355:

352:Partitioning

341:

329:

307:

304:

287:

269:Partitioning

254:

222:One can use

221:

202:

181:

176:

172:

168:

164:

160:

153:

147:

134:

128:

113:

104:

94:

87:

80:

73:

61:

49:Please help

44:verification

41:

2469:competition

2426:Slow design

2376:Form factor

2346:Concept art

2155:HTML editor

1835:Sustainable

1670:For testing

1514:By contract

1370:Work design

1345:Drug design

1317:engineering

1191:Icon design

1169:Game design

1147:Interaction

1095:Sustainable

1028:Sustainable

917:Type design

894:Photography

889:News design

832:Book design

827:Advertising

806:Disciplines

636:, pp. 6-10.

205:full custom

173:Fabrication

148:Modern day

2629:Wiktionary

2622:Wikisource

2576:technology

2546:principles

2145:Storyboard

1971:management

1966:leadership

1931:Privacy by

1770:Parametric

1740:Metadesign

1710:Integrated

1700:High-level

1685:Generative

1680:Functional

1549:Continuous

1544:Contextual

1519:C-K theory

1479:Approaches

1221:Web design

1075:CMF design

1055:Industrial

913:Typography

592:References

439:synthesis.

435:placement.

247:A typical

77:newspapers

2615:Wikiquote

2601:Wikibooks

2551:rationale

2516:knowledge

2491:education

2411:OODA loop

2135:Prototype

2120:Flowchart

2078:Blueprint

1946:computing

1882:Universal

1830:Safe-life

1735:Low-level

1725:Iterative

1705:Inclusive

1690:Geodesign

1581:Defensive

1529:Co-design

1499:Affective

679:215840278

554:photomask

405:Placement

272:Placement

199:Divisions

2645:Category

2608:Wikinews

2541:paradigm

2521:language

2501:engineer

2496:elements

2486:director

2171:property

2016:thinking

2006:strategy

1991:research

1951:controls

1909:Empathic

1840:Systemic

1800:Rational

1755:New Wave

1569:Critical

792:Designer

738:, p. 26.

575:See also

2594:Commons

2566:studies

2511:history

2479:student

2464:classic

2452:Design

2366:.design

2294:Graphex

1996:science

1986:pattern

1981:methods

1956:culture

1939:Design

1750:Modular

1603:Diffuse

1524:Closure

1246:Ceramic

904:Signage

787:Outline

506:routing

500:Routing

278:Routing

91:scholar

2571:studio

2556:review

2536:museum

2459:change

2267:Awards

2140:Sketch

2125:Mockup

2105:CAutoD

2046:Awards

2011:theory

2001:sprint

1976:marker

1941:choice

1315:&

1313:design

1149:design

1057:design

939:design

857:Motion

819:design

776:Design

734:

710:

677:

667:

632:

608:

233:Altera

93:

86:

79:

72:

64:

2454:brief

2341:Agile

2060:Tools

2037:Tools

1675:For X

1311:Other

1230:Other

675:S2CID

387:speed

347:Steps

98:JSTOR

84:books

2531:load

2526:life

2506:firm

2093:CAID

1961:flow

1877:TRIZ

1765:Open

732:ISBN

708:ISBN

665:ISBN

630:ISBN

606:ISBN

586:BEOL

581:FEOL

385:and

383:area

257:ASIC

249:ASIC

228:FPGA

224:ASIC

159:and

156:HDLs

70:news

2088:CAD

2068:AAD

1845:SOD

1825:RWD

1695:HCD

1162:EED

1011:EID

724:doi

657:doi

622:doi

492:In

465:CTS

320:SOI

235:).

216:DFM

185:DRC

175:or

163:or

129:In

53:by

2647::

730:,

673:.

663:.

641:^

628:,

314:nm

310:μm

133:,

768:e

761:t

754:v

726::

681:.

659::

624::

463:(

308:2

120:)

114:(

109:)

105:(

95:·

88:·

81:·

74:·

47:.

20:)

Text is available under the Creative Commons Attribution-ShareAlike License. Additional terms may apply.